МОДУЛЬ БОЙЫНША БӨЛУ ҚҰРЫЛҒЫСЫНЫҢ ӘРЕКЕТТІК МОДЕЛІН ЖОБАЛАУ ЖӘНЕ ЗЕРТТЕУ.

DOI:

https://doi.org/10.31489/2020No1/151-156Кілт сөздер:

асимметриялық криптоалгоритмдер, аппараттық шифрлау, модульдік редукция, әрекеттік моделі, жобалау.Аңдатпа

"CAD Quartus Prime Lite Edition бағдарламасында құрылғының оңтайлы шығындармен модуль бойынша бөлу құрылғысының әрекеттік моделі әзірленді. Жұмыс алгоритмі Verilog HDL тілінде жүзеге асырылған. Әрбір есептеу қадамында модульдің үш еселік, екі еселік немесе жалғыз мәнінің екі таңбаға жылжыған жоғарғы белгілік биттерден шегеріледі. Мысалдарды пайдалана отырып, әрекет моделінің алгоритмін функциялық және уақыт бойынша модельдеу орындалды және алгоритмнің дұрыстығы дәлелденді. Altera FPGA Cyclone VE 5CEBA4F23C7 арналған регистрларды жіберу деңгейдегі (RTL) құрылғы диаграммасы алынды. Уақыт талдауы әртүрлі жұмыс жағдайындағы принциптік және әрекеттік модельдері үшін максималды тактілік жиілігін анықтау үшін уақыт талдағышының көмегімен жүргізілді. "

References

"1 Hars L., Joye M., Quisquater J. Long Modular Multiplication for Cryptographic Applications. Cryptographic Hardware and Embedded Systems. CHES 2004, Lecture Notes in Computer Science, 2004, Issue 3156, pp. 45 – 61.

Petrenko V.I., Sidorchuk A.V., Kuz'minov J.V. Device for generating remainder with arbitrary modulus: pat. 2368942 С2 Russian Federation. No. 2007124282/09; Publ. 27.09.2009, Bull. No. 27, 9 p.

Pankratova I.A. Number-theoretical methods of cryptography. Tomsk, Tomsk State University, 2009, 120 p.

Zakharov V.M., Stolov E.L., Shalagin S/V. Apparatus for generating remainder for given modulo: pat 2421781 С1 Russian Federation.No. 2009138613/08; Publ. 20.06.2011, Bull. No. 17, 9 p.

Kopytov V.V., Petrenko V.I., Sidorchuk A.V. Device for generating remainder from arbitrary modulus of numbe. Pat. 2445730 С2 Russian Federation. No.2010106685/08; Publ. 20.03.2012, Bull. No.8, 8p.

Skryabin I., Sahin Y.H. Support operations for encryption algorithms with public key and their implementation in the microprocessor Elbrus. 2013. Available at: www.myshared.ru/ slide/213088

Eran Pisek, Plano, T.X., Th.M. Henige, Dallas, T.X. Method and apparatus for efficient modulo multiplication: pat. No. 8417756 B2 United States. No.12/216,896; Publ. 09.04.2013, 12 p.

Aitkhozhayeva Y. Zh., Tynymbayev S.T. Aspects of hardware reduction modulo in asymmetric cryptography. Bulletin of National Academy of Sciences of the Kazakhstan. 2014, No. 5(375), pp. 88 – 93.

Markus Bockes, Munich (DE); Jurgen Pulkus, Munich (DE) Method for arbitrary-precision division or modular reduction: pat. 9042543 B2 United States. No. 13/885, 878; Publ. 26.05.2015, 12p.

Yu H., Bai G., Hao J., Wang C. Yap Efficient Modular Reduction Algorithm Without Correction Phase. Frontiers in Algorithmics. Lecture Notes in Computer Science, 2015, Vol. 9130, pp. 304 – 313.

Tynymbayev S.T., Aitkhozhayeva Y.Zh. The remainder generator by an arbitrary modulus of the number: pat. 30983 The Republic of Kazakhstan. No. 014/1450.1; Published 15.03.2016, 5 p.

Kovtun M., Kovtun V. Review and classification of algorithms for dividing and modulating large integers for cryptographic applications. 2017. Available at: http://docplayer.ru/30671408-Obzor-i-klassifikaciya-algoritmov-deleniya

Tynymbayev S.T., Aitkhozhayeva Y.Zh, Adilbekkyzy S. High speed device for modular reduction. Bulletin of National Academy of Sciences of the Republic of Kazakhstan. 2018, No. 6 (376), pp. 147 – 152.

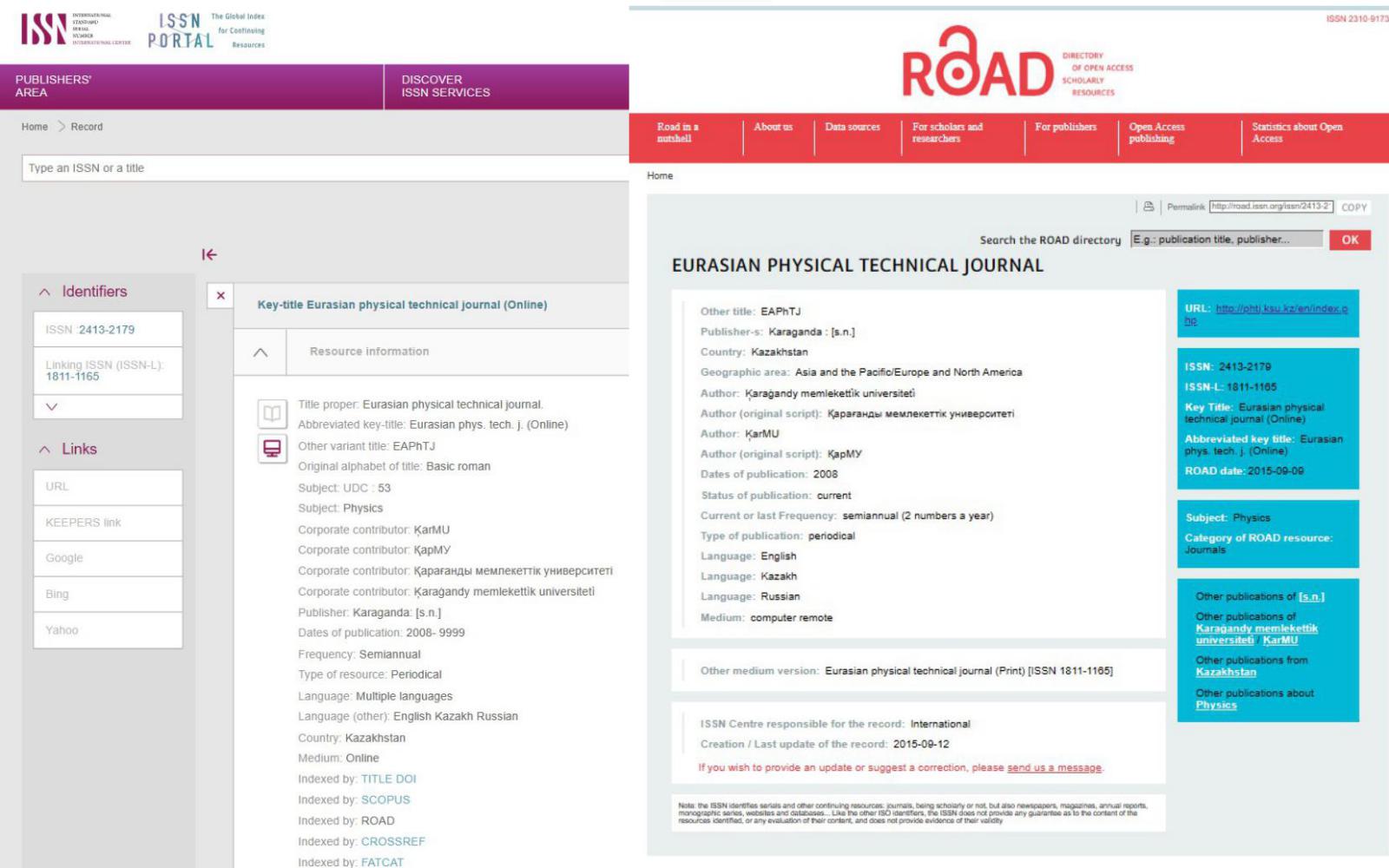

Adilbekkyzy S. Aitkhozhayeva Y.Zh., Tynymbayev S.T. Modeling of the partial reminder former of the modular reduction device. Eurasian Union of Scientists. 2019, Vol. 6 (63), pp. 47 – 51.

Tynymbayev S.T., Aitkhozhayeva Y.Zh, Adilbekkyzy S., et al. Development and modeling of schematic diagram for the modular reduction device. Problems of Informatics, 2019, No. 4, pp.42 – 52.

Kramarov S.O., Mityasova O.Yu., Sokolov S.V., Tishchenko E.N., Shevchuk P.S. Cryptographic information security. Moscow: RIOR Publishing Center, 2018, 322 p.

"